# Implementer's Guide to the CAESAR Hardware API

Ekawat Homsirikamol, William Diehl, Ahmed Ferozpuri, Farnoud Farahmand, and Kris Gaj

Electrical and Computer Engineering Department,

George Mason University

Fairfax, Virginia 22030

{ehomsiri, wdiehl, aferozpu, ffarahma, kgaj}@gmu.edu

June 10, 2016

### Contents

| 1 | Introduction                                                                                                                                                   | 4                                |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 2 | Top-level Block Diagram of a High-Speed Implementation2.1 PreProcessor2.2 PostProcessor2.3 CMD FIFO                                                            | 6<br>9<br>10<br>11               |

| 3 | The Development and Benchmarking of High-Speed and Lightweight Implementations                                                                                 | 12                               |

| 4 | The AEAD Configuration 4.1 High-Speed Implementations                                                                                                          | 14<br>14<br>15                   |

| 5 | CipherCore Development for High-Speed Implementations5.1Interface5.2Handshakes5.3Design Procedure5.4Dummy Authenticated Ciphers5.5AES and Keccak Permutation F | 18<br>18<br>23<br>24<br>27<br>31 |

| 6 | Test Vector Generation                                                                                                                                         | 33                               |

| 7 | Simulation                                                                                                                                                     | 35                               |

| 8 | Generation and Publication of Results                                                                                                                          | 36                               |

| A | The Supporting Package Description                                                                                                                             | 37                               |

| CONTENTS | 3 |

|----------|---|

| CONTENTS | 3 |

| $\mathbf{B}$ | Installation of Libraries and Tools |                           |    |  |  |  |  |  |

|--------------|-------------------------------------|---------------------------|----|--|--|--|--|--|

|              | B.1                                 | Interpreter and compiler  | 39 |  |  |  |  |  |

|              | B.2                                 | OpenSSL Installation      | 40 |  |  |  |  |  |

|              | B.3                                 | Python module (aeadtvgen) | 41 |  |  |  |  |  |

| Bi           | bliog                               | raphy                     | 42 |  |  |  |  |  |

### 1 Introduction

The CAESAR Hardware API [1] is intended to meet the requirements of all algorithms submitted to the CAESAR competition, as well as many earlier developed authenticated ciphers, such as AES-GCM, AES-CCM, etc. The major parts of its specification [1] include the minimum compliance criteria, interface, communication protocol, and timing characteristics supported by the core. All of these parts have been defined with the goals of guaranteeing (a) compatibility among implementations of the same algorithm developed by different designers, and (b) fair benchmarking of authenticated ciphers in hardware.

Our proposed API is suitable for both high-speed and lightweight implementations of authenticated ciphers. The only difference at the API level is the width of Public Data Input (PDI) and Data Output (DO) ports, which is defined as follows:

```

Lightweight implementations: w = 8, 16, 32

High-speed implementations: 32 \le w \le 256.

```

From the Implementer's point of view, this difference is important, as small values of w (used in lightweight implementations) imply that any preprocessing (such as padding) and any postprocessing (such as zeroization of unused bytes) are significantly easier to implement compared to the case of large values of w (used in high-speed implementations).

As a result, we leave the internal structure of any lightweight implementation entirely to the designers of such implementations. The only support we provide to the designers of lightweight implementations is in the areas of test vector generation (Chapter 6), simulation (Chapter 7), as well as result generation and publication (Chapter 8).

On the other hand, for the designers of high-speed implementations, we provide the following support:

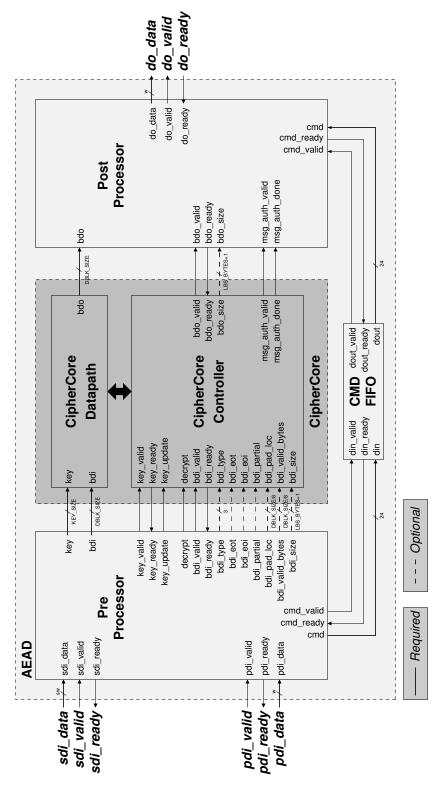

• universal top-level block diagram (see Fig. 2.1)

- universal VHDL code for the PreProcessing unit

- universal VHDL code for the PostProcessing unit

- hardware API for the heart of the design, called CipherCore

- implementer's guide to designing any specific CipherCore

- VHDL code for the three dummy CipherCores following the CipherCore API

Below we describe all these supporting materials one by one. It should be stressed that the high-speed implementations of authenticated ciphers compliant with the CAESAR hardware API can be also developed without using any resources described in this document, by just following directly the specification of the CAESAR API [1].

## 2 Top-level Block Diagram of a High-Speed Implementation

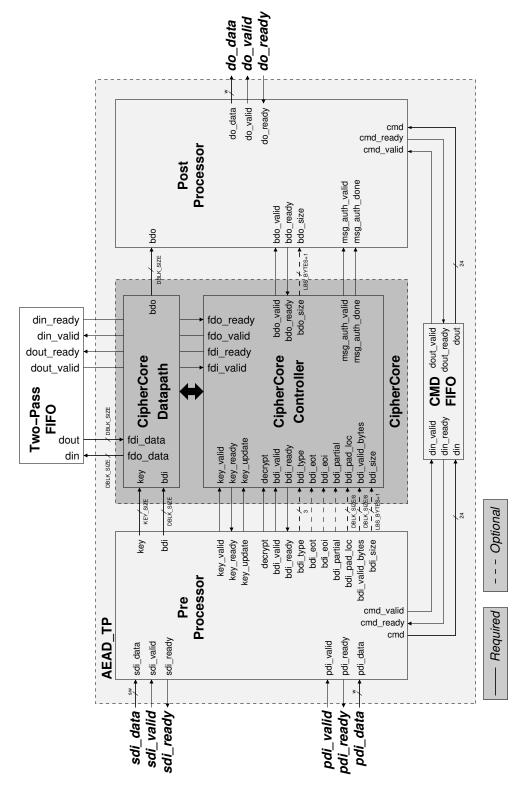

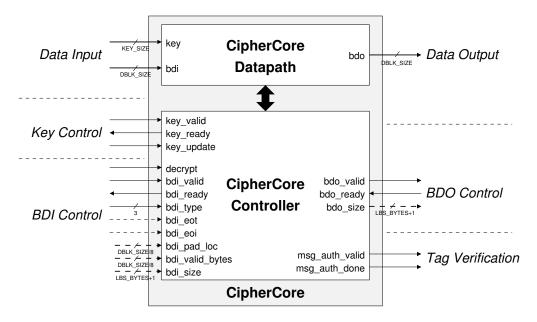

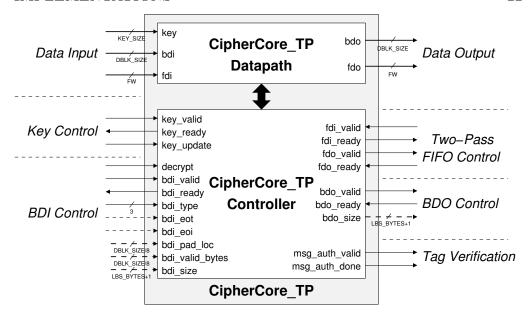

The proposed top-level block diagram of a high-speed, non-pipelined implementation of a *single-pass* authenticated cipher compliant with the CAE-SAR hardware API is shown in Fig. 2.1. The corresponding block diagram for a *two-pass* authenticated cipher is shown in Fig. 2.2. The only difference are ports used for communication with an external Two-Pass FIFO, used to store an output from the first pass of an implemented algorithm.

In each case, the top-level unit is divided into four lower-level units, called PreProcessor, PostProcessor, Command (CMD) FIFO, and Cipher-Core. The universal VHDL codes of the first three units are designed to be suitable for all authenticated ciphers to be implemented as a part of the CAESAR benchmarking project. These codes are provided as a part of the supporting package [2]. Due to the availability of this package as well as the well-defined hardware API of the CipherCore itself (described in Chapter 5), the implementers of any specific authenticated cipher do not need to be concerned with the internal details of the PreProcessor, PostProcessor, and CMD FIFO.

Because of the availability of the open source code for the PreProcessor, PostProcessor, and CMD FIFO, the designers of high-speed implementations of authenticated ciphers can focus exclusively on the development of the CipherCore unit, which can be further separated into its own datapath and controller, if desired.

Below is a high-level description of major functions of these units.

Figure 2.1: Top-level block diagram of a high-speed architecture of a single-pass authenticated cipher core, AEAD

Figure 2.2: Top-level block diagram of a high-speed architecture of a two-pass authenticated cipher core, AEAD\_TP

9

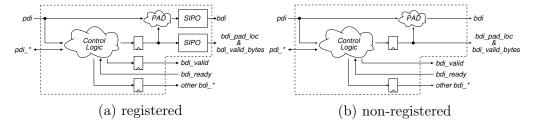

Figure 2.3: The PreProcessor Design. SIPO = Serial-In Parallel-Out unit. pdi\_\* and bdi\_\* stand for all PreProcessor ports, shown in Fig. 2.1, with the names starting from the respective strings.

#### 2.1 PreProcessor

The PreProcessor is responsible for the execution of the following tasks common for majority of CAESAR candidates:

- parsing segment headers

- loading and activating keys

- Serial-In-Parallel-Out loading of input blocks

- padding input blocks, and

- keeping track of the number of data bytes left to process.

An overview of the PreProcessor design is shown Fig. 2.3. This unit can be configured to operate in two modes, registered and non-registered. The choice between these modes is made based on the width of public data input, PDI, (denoted as w in Fig. 2.1) and the size of an input block (denoted as  $DBLK\_SIZE$  in Fig. 2.1).

In a typical scenario, where the size of an input block is larger than the width of PDI, w, the PreProcessor operates in the registered mode. If the width of PDI is the same as the size of an input block, the non-registered mode should be used. The non-registered mode ensures a high-throughput operation for algorithms that require a new block of data every clock cycle. It must be noted that operating the design in non-registered mode may affect the overall maximum clock frequency of the design due to additional critical path associated with the padding logic (if used).

### CHAPTER 2. TOP-LEVEL BLOCK DIAGRAM OF A HIGH-SPEED IMPLEMENTATION 10

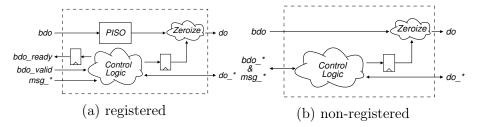

Figure 2.4: The PostProcessor Design. PISO = Parallel-In Serial-Out unit. msg\_\*, bdo\_\*, and do\_\* stand for all PostProcessor ports, shown in Fig. 2.1, with the names starting from the respective strings.

#### 2.2 PostProcessor

The PostProcessor is responsible for the following tasks:

- clearing any portions of output blocks not belonging to the ciphertext or plaintext

- Parallel-In-Serial-Out conversion of output blocks into words

- formatting output words into segments

- generating the status block with the result of authentication.

An overview of the PostProcessor design is shown Fig. 2.4. This unit can be configured to operate in either registered or non-registered mode. The choice is made based on the dependence between the size of an output block (equal to the size of an input block) and the width of the data out, DO port (equal to width of public data input, PDI). Namely, when an output block size is larger than the width of DO, the registered mode is preferable. Otherwise, the non-registered mode should be used. Similarly to the PreProcessor design, when the unit operates in the non-registered mode, the maximum clock frequency maybe be affected.

The PreProcessor and PostProcessor units are highly configurable using generics of AEAD. These generics can be used, for example, to determine:

- the widths of the pdi, sdi, and do ports

- the size of the associated data block, message/ciphertext block, key, and tag

• padding for the associated data and the message.

They have been designed to assure:

- Ease of use

- No influence on the maximum clock frequency of AEAD (up to 300 MHz in Virtex 7)

- Limited area overhead.

#### 2.3 CMD FIFO

The Command (CMD) FIFO is a small 4x24 First-Word-Fall-Through (FWFT) FIFO that temporarily stores all significant bits of instructions and segment headers that need to be passed to the output. This module allows the Pre-Processor to operate with the maximum efficiency. This FIFO's width is selected based on the fact that the instructions defined in [1], Fig. 7, contain only 4 significant bits, and segment headers, defined in [1], Fig. 8, contain only 24 significant bits.

# 3 The Development and Benchmarking of High-Speed and Lightweight Implementations

The development and benchmarking of a **high-speed** implementation of a selected authenticated cipher can be performed using the following major steps, described in the subsequent chapters of this guide:

- 1. Configure the provided AEAD entity declaration for high-speed implementations (Chapter 4)

- 2. Develop CipherCore (Chapter 5)

- 3. Generate test vectors (Chapter 6)

- 4. Verify the AEAD design (including the CipherCore design) using functional simulation (Chapter 7)

- 5. Generate optimized results for AEAD using FPGA tools (Chapter 8).

The development and benchmarking of a **lightweight** implementation of a selected authenticated cipher can be performed using the following major steps, described in the subsequent chapters of this guide:

- 1. Configure the provided AEAD entity declaration for lightweight implementations (Chapter 4)

- 2. Develop the entire AEAD core from scratch, based on the CAESAR Hardware API specification [1]

- 3. Generate test vectors (Chapter 6)

### CHAPTER 3. THE DEVELOPMENT AND BENCHMARKING OF HIGH-SPEED AND LIGHTWEIGHT IMPLEMENTATIONS

- 4. Verify the AEAD design using functional simulation (Chapter 7)

- 5. Generate optimized results for AEAD using FPGA tools (Chapter 8).

13

As can be seen from the above description, only the first two steps are different. All remaining steps are universal and apply to both high-speed and lightweight implementations.

### 4 The AEAD Configuration

#### 4.1 High-Speed Implementations

The entity declaration of AEAD for high-speed implementations is available as a part of the supporting package in the file

\$ROOT/hardware/AEAD/src\_rtl\_hs/AEAD.vhd

This entity declaration contains multiple generics defined in Table 4.1. Additional generics, used to determine the desired padding scheme are defined in Tables 4.2 and 4.3. The names of all generics, listed in the aforementioned tables, are supplemented in the VHDL code with the prefix G\_.

The following restrictions must be considered when configuring the AEAD entity for high-speed implementations:

#### 4.1.1 I/O Port Widths

Consistently with the specification of the CAESAR hardware API, the allowed values of the port widths for high-speed implementations are as follows:

$$32 \le w \le 256,$$

$32 \le sw \le 64.$

These widths are described in the AEAD entity declaration using generics W and SW.

#### 4.1.2 Block sizes

Values of generics ABLK\_SIZE and DBLK\_SIZE, describing the sizes of input blocks for associated data and message/ciphertext, respectively, must be multiples of the generic W. Similarly, the generic KEY\_SIZE must be

a multiple of the generic SW. Additionally, ABLK\_SIZE is assumed to be smaller than or equal to DBLK\_SIZE.

# 4.1.3 The Preprocessor and PostProcessor Maximum Input/Output Rates

The maximum rate at which the PreProcessor can provide a block of data and the PostProcessor can accept a block of data is dependent on the size of the message/ciphertext block (DBLK\_SIZE) and the I/O port width (W). In the registered mode of operation, a new block of input data can be provided by the PreProcessor and accepted by the PostProcessor every  $DBLK_SIZE/W+1$  clock cycles. In the non-registered mode, a new block of input data can be provided by the PreProcessor and accepted by the PostProcessor every clock cycle.

#### 4.2 Lightweight Implementations

The entity declaration of AEAD for lightweight implementations is available as a part of the supporting package in the file

\$ROOT/hardware/AEAD/src\_rtl\_lw/AEAD.vhd

This entity declaration contains only values of generics  $G_W$  and  $G_SW$ , used to determine the I/O port widths, w and sw, respectively. Consistently with the specification of the CAESAR hardware API, the allowed values of these port widths are as follows:

$$w = 8, 16, 32,$$

$sw = 8, 16, 32.$

Table 4.1: AEAD Generics

| Generic            | Type    | Default<br>Value | Definition                                          |  |  |  |  |

|--------------------|---------|------------------|-----------------------------------------------------|--|--|--|--|

|                    |         |                  |                                                     |  |  |  |  |

| I/O Widths in Bits |         |                  |                                                     |  |  |  |  |

| W                  | Integer | 32               | Public data input and data output width             |  |  |  |  |

| SW                 | Integer | 32               | Secret data input width                             |  |  |  |  |

|                    |         |                  | set Behavior                                        |  |  |  |  |

| ASYNC_RSTN         | Boolean | False            | Reset behavior. True=Asynchronous active low,       |  |  |  |  |

|                    |         |                  | False= Synchronous active high.                     |  |  |  |  |

|                    |         | Spe              | ecial Features                                      |  |  |  |  |

| ENABLE_PAD         | Boolean | False            | Enable padding (See additional settings in Tables   |  |  |  |  |

|                    |         |                  | 4.2 and 4.3)                                        |  |  |  |  |

| CIPH_EXP           | Boolean | False            | Ciphertext expansion mode. This option should       |  |  |  |  |

|                    |         |                  | be used when the ciphertext size is not the same    |  |  |  |  |

|                    |         |                  | as the plaintext size, i.e., the ciphertext is ex-  |  |  |  |  |

|                    |         |                  | panded. It should also be used when Cipher-         |  |  |  |  |

|                    |         |                  | text=Ciphertext  Tag.                               |  |  |  |  |

| REVERSE_CIPH       | Boolean | False            | Reverse ciphertext mode. Used, for example, by      |  |  |  |  |

|                    |         |                  | PRIMATEs-APE, currently not supported.              |  |  |  |  |

| MERGE_TAG          | Boolean | False            | No tag segment. This parameter should be set to     |  |  |  |  |

|                    |         |                  | True when the CipherCore does not separate Tag      |  |  |  |  |

|                    |         |                  | from Ciphertext, i.e., Ciphertext=Ciphertext  Tag.  |  |  |  |  |

|                    |         | Block Size       | Parameters in Bits                                  |  |  |  |  |

| ABLK_SIZE          | integer | 128              | Associated data block size. This value should be    |  |  |  |  |

|                    |         |                  | smaller than or equal to DBLK_SIZE.                 |  |  |  |  |

| DBLK_SIZE          | integer | 128              | Data (message/ciphertext) block size                |  |  |  |  |

| KEY_SIZE           | integer | 128              | Key size                                            |  |  |  |  |

| TAG_SIZE           | integer | 128              | Tag size. Note: This value is not used when         |  |  |  |  |

| _                  |         |                  | MERGE_TAG is True.                                  |  |  |  |  |

|                    |         | Padd             | ing Parameters                                      |  |  |  |  |

| PAD_STYLE          | integer | 1                | Padding style. See Table 4.2.                       |  |  |  |  |

| PAD_AD             | integer | 1                | Padding behavior for associated data. See Table 4.3 |  |  |  |  |

| PAD_D              | integer | 1                | Padding behavior for message. See Table 4.3.        |  |  |  |  |

Table 4.2: Extended description of PAD STYLE.

| Value   Description |                      |  |  |  |  |  |

|---------------------|----------------------|--|--|--|--|--|

| 0                   | No padding           |  |  |  |  |  |

| 1                   | 10* padding rule     |  |  |  |  |  |

| 2                   | ICEPOLE padding rule |  |  |  |  |  |

Table 4.3: Parameters of PAD\_AD and PAD\_D. A = Pad enable. B = Extra block is added when AD/D is empty. C = Extra block is added when AD/D is a non-zero multiple of a block size.

| Value | Feature |   |              |  |  |  |

|-------|---------|---|--------------|--|--|--|

|       | A       | В | $\mathbf{C}$ |  |  |  |

| 0     |         |   |              |  |  |  |

| 1     | X       |   |              |  |  |  |

| 2     | X       | X |              |  |  |  |

| 3     | X       |   | X            |  |  |  |

| 4     | X       | X | X            |  |  |  |

## 5 CipherCore Development for High-Speed Implementations

#### 5.1 Interface

Figure 5.1: CipherCore

The interface of CipherCore is shown in Figure 5.1. Ports marked using dashed lines are optional and used only if required. This approach allows the synthesis tool to trim the unused ports and the associated logic from the design, resulting in a better resource utilization.

Data input ports are limited to key and bdi (block data input). The key port is controlled using the key valid and key ready handshake signals.

key\_update is used to notify the CipherCore that it should update the internal key prior to processing the next message.

Similarly to the *key* port, the *bdi* port is controlled using the *bdi\_valid* and *bdi\_ready* handshake signals. The *decrypt* signal informs the core whether the current operation is encryption or decryption. The *bdi\_type* input indicates the type of input data, with the encoding shown in Table 5.1. It must noted that all ports of the BDI communication group and *bdi* are synchronized with the *bdi\_valid* input. Their values should be read only when the *bdi\_valid* signal is high.

| Encoding | Type                                       |

|----------|--------------------------------------------|

| 00-      | Associated Data                            |

| 01-      | ${\it Message/Ciphertext/Ciphertext  Tag}$ |

| 100      | Tag                                        |

| 101      | Length                                     |

| 110      | Public message number                      |

| 111      | Secret message number                      |

Table 5.1: bdi type Encoding. – represents don't care.

The same scenario also applies to the block data output port (bdo) and its associated control signals, which are synchronized with the value of the bdo\_valid output. bdo\_size is not used unless the CIPH\_EXP generic of AEAD is set to True. When this is the case, each active value of bdo\_valid must be accompanied by providing the size of an output block, in bytes, using the bdo\_size port.

The message authentication ports  $(msg\_auth\_*)$  are only used during the authenticated decryption operation, when the core must provide output signals indicating whether the authentication is done and the result is (or is not) valid. Note that  $msg\_auth\_valid$  signal is synchronized with  $msg\_auth\_done$  signal.

Port descriptions are provided in Table 5.2. Ports related to bdi control are categorized according to the following criteria:

#### COMM A handshake signal.

INPUT INFO An auxiliary signal that remains valid until a given input is fully processed. Deactivation is typically done at the end of input.

Table 5.2: CipherCore Port Descriptions. LBS\_BYTES =  $\log_2(DBLK\_SIZE/8)$

| Name                | Direction | Size          | Description                                                                                  |  |  |  |  |  |

|---------------------|-----------|---------------|----------------------------------------------------------------------------------------------|--|--|--|--|--|

| Data Input & Output |           |               |                                                                                              |  |  |  |  |  |

| key                 | in        | KEY_SIZE      | Key data                                                                                     |  |  |  |  |  |

| bdi                 | in        | DBLK_SIZE     | Block data input                                                                             |  |  |  |  |  |

| bdo                 | out       | DBLK_SIZE     | Block data output                                                                            |  |  |  |  |  |

|                     |           | Key Con       | atrol                                                                                        |  |  |  |  |  |

| key_valid           | in        | 1             | Key data is valid                                                                            |  |  |  |  |  |

| key_ready           | out       | 1             | CipherCore is ready to receive a new key                                                     |  |  |  |  |  |

| key_update          | in        | 1             | Key must be updated prior to processing a new                                                |  |  |  |  |  |

|                     |           |               | input                                                                                        |  |  |  |  |  |

|                     |           | BDI Cor       | ntrol                                                                                        |  |  |  |  |  |

| decrypt             | in        | 1             | [INPUT INFO] 0=Encryption, 1=Decryption                                                      |  |  |  |  |  |

| bdi_valid           | in        | 1             | [COMM] BDI data is valid                                                                     |  |  |  |  |  |

| bdi_ready           | out       | 1             | [COMM] CipherCore is ready to receive data                                                   |  |  |  |  |  |

| bdi_type            | in        | 3             | [BLOCK INFO] Type of BDI data. See Ta-                                                       |  |  |  |  |  |

|                     |           |               | ble 5.1.                                                                                     |  |  |  |  |  |

| bdi_eot             | in        | 1             | [BLOCK INFO] The current BDI block is the                                                    |  |  |  |  |  |

|                     |           |               | last block of its type. Note: Only applies when                                              |  |  |  |  |  |

| 1 1                 |           | 1             | the type is either AD, Message, or Ciphertext.                                               |  |  |  |  |  |

| bdi_eoi             | in        | 1             | [BLOCK INFO] The current BDI block is the                                                    |  |  |  |  |  |

|                     |           |               | last block of input other than a block of the<br>Length segment, a block of the Tag segment, |  |  |  |  |  |

|                     |           |               | or a block of padding.                                                                       |  |  |  |  |  |

| bdi_partial         | in        | 1             | [SEGMENT INFO] The current block is either                                                   |  |  |  |  |  |

|                     |           | _             | a partial block of AD or Message, or the re-                                                 |  |  |  |  |  |

|                     |           |               | sult of encryption of a partial message block.                                               |  |  |  |  |  |

|                     |           |               | Note: This optional signal is used only in the                                               |  |  |  |  |  |

|                     |           |               | implementations of the ciphertext expansion                                                  |  |  |  |  |  |

|                     |           |               | algorithms. We are aware of its necessity only                                               |  |  |  |  |  |

|                     |           |               | for the implementation of the Round 2 AES-                                                   |  |  |  |  |  |

|                     |           |               | COPA.                                                                                        |  |  |  |  |  |

| bdi_pad_loc         | in        | DBLK_SIZE/8   | [BLOCK INFO] Encoding of the byte location                                                   |  |  |  |  |  |

|                     |           | DDIII GIAL (  | where padding begins. See Table 5.3.                                                         |  |  |  |  |  |

| bdi_valid_bytes     | in        | DBLK_SIZE/8   | [BLOCK INFO] Encoding of the byte locations                                                  |  |  |  |  |  |

| Lai -i              | •         | LBS BYTES+1   | that are valid. See Table 5.3.                                                               |  |  |  |  |  |

| bdi_size            | in        |               | [BLOCK INFO] Number of valid bytes in bdi.                                                   |  |  |  |  |  |

| 7.1                 |           | BDO Cor       |                                                                                              |  |  |  |  |  |

| bdo_valid           | out       | 1             | BDO data is valid                                                                            |  |  |  |  |  |

| bdo_ready           | in        | 1 LDC DVTDC+1 | PostProcessor is ready to receive data.                                                      |  |  |  |  |  |

| bdo_size            | out       | LBS_BYTES+1   | Number of valid bytes in bdo. This port <b>must</b> be used when <i>CIPH EXP</i> is active.  |  |  |  |  |  |

|                     |           |               | _                                                                                            |  |  |  |  |  |

| (1 3:1              | , ,       | Tag Verific   |                                                                                              |  |  |  |  |  |

| msg_auth_valid      | out       | 1             | 1=Authentication success, 0=Authentication                                                   |  |  |  |  |  |

| mag auth dona       | out       | 1             | failure Authentication done                                                                  |  |  |  |  |  |

| msg_auth_done       | out       | 1             | Authentication done                                                                          |  |  |  |  |  |

- SEGMENT INFO An auxiliary signal that remains valid for the current segment. Its value changes when a new segment is received via the PDI data bus.

- BLOCK INFO An auxiliary signal that is valid for the current input block. Its value changes when a new block is read.

The correct values of bdi\_valid\_bytes, bdi\_pad\_loc, and bdi\_size for various numbers of valid bytes within a 4-byte data block are shown in Table 5.3, where:

- Case A: Either not the last block or the last block with all 4 bytes valid.

- Case B: The last block with 3 bytes valid.

- Case C: The last block with 1 byte valid.

- Case D: The last block with no valid bytes. Assuming the 10\* padding, this block consists of a single 1 followed by 31 zeros.

Table 5.3: Values of the special control signals  $bdi_valid_bytes$ ,  $bdi_pad_loc$ , and  $bdi_size$  for the bdi bus with the width w=32. Byte Validity represents the byte locations in bdi that were the part of input (e.g., AD or message) before padding.

| Byte/Bit Position  |   | 2      | 1   | 0 | 3 | 2      | 1   | 0 |  |

|--------------------|---|--------|-----|---|---|--------|-----|---|--|

| Dyte/Dit i osition | ( | Case A |     |   |   | Case B |     |   |  |

| Byte Validity      |   |        |     |   |   |        |     |   |  |

| bdi_valid_bytes    | 1 | 1      | 1   | 1 | 1 | 1      | 1   | 0 |  |

| bdi_pad_loc        |   | 0      | 0   | 0 | 0 | 0      | 0   | 1 |  |

| bdi_size           |   | 1      | 0   | 0 |   | 0      | 1   | 1 |  |

|                    |   | Cas    | e C | ; | ( | Cas    | e D | ) |  |

| Byte Validity      |   |        |     |   |   |        |     |   |  |

| bdi_valid_bytes    | 1 | 0      | 0   | 0 | 0 | 0      | 0   | 0 |  |

| bdi_pad_loc        | 0 | 1      | 0   | 0 | 1 | 0      | 0   | 0 |  |

| bdi_size           |   | 0      | 0   | 1 |   | 0      | 0   | 0 |  |

For the CipherCore that supports Two-Pass algorithms, additional ports have been added to accommodate the communication with the external FIFO, as shown in Figure 5.2.

Figure 5.2: Two-Pass CipherCore

The additional port descriptions required for a CipherCore that supports Two-Pass algorithms are provided in Table 5.4. It must be noted that all the ports listed in Table 5.2 are also present in the interface of the Two-Pass core.

Table 5.4: Additional Port Descriptions for a Two-Pass CipherCore.

| Name      | Direction           | Size | ze Description                                |  |  |  |  |  |  |  |

|-----------|---------------------|------|-----------------------------------------------|--|--|--|--|--|--|--|

|           | Data Input & Output |      |                                               |  |  |  |  |  |  |  |

| fdi_data  | in                  | FW   | Input data from the two-pass FIFO             |  |  |  |  |  |  |  |

| fdo_data  | out                 | FW   | Output data to the two-pass FIFO              |  |  |  |  |  |  |  |

|           | Control             |      |                                               |  |  |  |  |  |  |  |

| fdi_valid | in                  | 1    | fdi data is valid                             |  |  |  |  |  |  |  |

| fdi_ready | out                 | 1    | CipherCore is ready to receive a new two-pass |  |  |  |  |  |  |  |

|           |                     |      | data                                          |  |  |  |  |  |  |  |

| fdo_valid | out                 | 1    | CipherCore is ready to send a new two-pass    |  |  |  |  |  |  |  |

|           |                     |      | data                                          |  |  |  |  |  |  |  |

| fdo_ready | in                  | 1    | two-pass FIFO is ready to receive a new data  |  |  |  |  |  |  |  |

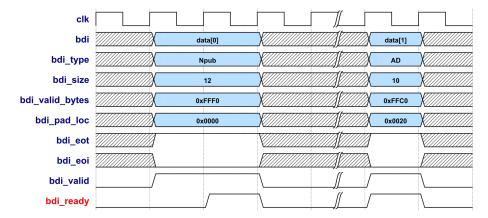

Figure 5.3: An example of a handshake used for loading data using the input bdi

#### 5.2 Handshakes

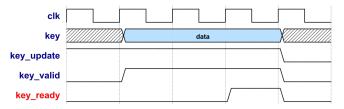

This section presents examples of handshakes. All ports in the figures of this section are represented by the blue and the red color, for input and output ports, respectively. Fig. 5.3 provides an example of a handshake used for loading a block of data using the (bdi) port. Data and its auxiliary signals are synchronized with the  $bdi\_valid$  signal. Similarly for key, data is synchronized with the  $key\_valid$  signal, as shown in Figure 5.4.

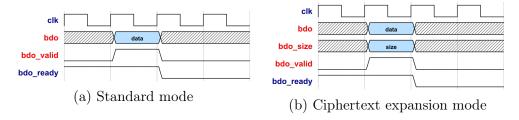

Fig. 5.5 provides an example of a handshake used to write output to the PostProcessor. Fig. 5.5a presents an example for the standard mode of operation of an authentiocated cipher. Figure 5.5b presents an example for the case of an algorithm operating in the ciphertext expansion mode. An additional output port ( $bdo\_size$ ) is now required to update the PostProcessor about the size of the current message block after decryption. This information is used by the PostProcessor to update the header with correct value of the last segment size.

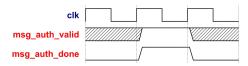

Finally, an example of a handshake for authentication is shown in Fig. 5.6. For every decryption operation, PostProcessor should issue the  $msg\_auth\_done$  signal to indicate the completion of the authentication check. At the same time,  $msg\_auth\_valid$  is captured by the PostProcessor to determine the result of authentication. These two signals should only be activated once for every decryption. Subsequent values of the  $msg\_auth\_done$  signal during the same decryption operation are ignored.

Figure 5.4: An example of a handshake used for loading a key

Figure 5.5: An example of a handshake used for writing data in the a) Standard mode, b) Ciphertext expansion mode

Figure 5.6: An example of a handshake used to perform message authentication

#### 5.3 Design Procedure

It is recommended that you start the development of the CipherCore, specific to a given authenticated cipher, by using the code provided in the Development Package, in the folder

\$ROOT/hardware/AEAD/src rtl hs

In particular, the appropriate connections among the CipherCore, the Pre-Processor, the PostProcessor, and the CMD FIFO modules are already specified in this code. A designer needs to modify generics in the AEAD module, and then develop the CipherCore Datapath and the CipherCore Controller.

The development of the CipherCore is left to individual designers and can be performed using their own preferred design methodology. Typically, when using a traditional RTL (Register Transfer Level) methodology, the

25

CipherCore Datapath is first modeled using a block diagram, and then translated to a hardware description language (VHDL or Verilog HDL). The CipherCore Controller is then described using an algorithmic state machine (ASM) chart or a state diagram, further translated to HDL.

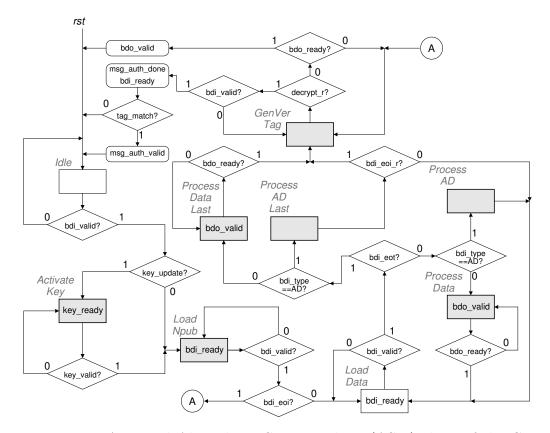

An ASM chart of the CipherCore Controller typically contains the following states:

- 1. Idle

- 2. Activate Key

- 3. Load Npub

- 4. Load Data

- 5. Process AD

- 6. Process AD Last

- 7. Process Data

- 8. Process Data Last

- 9. Generate/verify Tag (GenVer Tag).

An example ASM chart for the CipherCore Controller is shown Fig. 5.7. After a new instruction or after reset, the control should wait for the first block of data in the *Idle* state. The CipherCore should monitor the bdi\_valid for the first block of data, which is typically Npub. When this signal is active, the circuit should check whether the current key requires an update by inspecting the key\_update signal. If it does, the controller changes its state to *Activate Key*. In this state either a new key is stored internally within the CipherCore or the corresponding round keys are precomputed. Once this task is completed, key\_ready should be activated to acknowledge the key activation.

Once a new key is activated or no new key is required (key\_update=0), the circuit is ready to process the first block of data (Npub) in the Load Npub state. At the same time, that the Npub block is loaded into the Cipher-Core, the circuit needs to acknowledge its receipt by setting the bdi\_ready output to high. The controller then moves to the next processing state, Load Data. In the case that Npub is the last block of data (AD size = Message/Ciphertext size = 0), which can be determined using the bdi\_eoi input, the controller state can change directly to Generate/verify tag.

In the *Load Data* state, the circuit waits until the next input block is valid (bdi\_valid=1), and then processes data based on the incoming input

Figure 5.7: A typical Algorithmic State Machine (ASM) chart of the CipherCore Controller. Each shaded state in this diagram may need to be replaced by a sequence of states in the actual implementation of a complex authenticated cipher.  $*_r$  are status registers storing values of the respective inputs read during the last bdi handshake.

type (bdi\_type). Depending on the algorithm, additional processing may be required for the last block of data. This block can be determined using the end-of-type input (bdi\_eot). At the same time, the end-of-input signal (bdi\_eoi) may be stored in a register within the CipherCore to keep track of the last input state. This status register is useful to determine when no additional data block is expected after processing of the last AD block, so that the controller can progress to the last state (Generate/verify tag) directly.

In the last state, *Generate/verify tag*, during the authenticated encryption operation, the core should generate a new tag and pass it to the Post-Processor via the bdo bus. During the authenticated decryption operation, msg\_auth\_done should be activated, and the msg\_auth\_valid signal should be used to provide the result of authentication.

#### 5.4 Dummy Authenticated Ciphers

Five example designs of the CipherCore and AEAD, corresponding to five Dummy Authenticated Ciphers, are provided as a part of our distribution. The first three Dummy Authenticated Ciphers is specified using the following equations:

$$AD = AD_1, AD_2, ..., AD_{n-1}, AD_n$$

(5.1)

$$PT = PT_1, PT_2, ..., PT_{m-1}, PT_m$$

(5.2)

$$CT = CT_1, CT_2, ..., CT_{m-1}, CT_m$$

(5.3)

$$CT_i = PT_i \oplus i \oplus Key \oplus Npub$$

(5.4)

for  $i = 1..m - 1$ .

$$CT_m = Trunc(PT_m \oplus i \oplus Key \oplus Npub, PT_m)$$

(5.5)

$$CT_m = Pad(PT_m) \oplus m \oplus Key \oplus Npub$$

(5.6)

#### when **CIPH\_EXP**=True.

$$Tag = Key \oplus Npub \oplus Len \oplus \bigoplus_{i=1}^{n-1} AD_i \oplus Pad(AD_n) \oplus \bigoplus_{i=1}^{m-1} PT_i \oplus Pad(PT_m)$$

(5.7)

where,

- $PT_i$  and  $CT_i$  are the plaintext (message) and ciphertext blocks, respectively,

- $AD_i$  = associated data block,

- $Pad(\cdot)$  represents a padding operation applied to the last AD and/or the last plaintext block,

- Trunc(X, Y) truncates X to the size of Y,

- i = 128-bit block number,

- Key = 128-bit key,

- Npub = Public message number,

- Len = 64-bit associated data length (in bytes) || 64-bit plaintext length (in bytes).

For an XOR operation with inputs of different sizes, the smaller operands are appended with zeros to have the same length as the longest operand. The result has the length of the longest operand. All examples are based on a 128-bit data block, unless specified otherwise. The differences between each Dummy Authenticated Cipher are primarily based on the definition of padding and values of parameters described below. Please note that a typical padding behavior is either appending all zeros  $(0^*)$  or one followed by zeros  $(10^*)$ .

The design of the controllers used in our dummy cores is based on the ASM chart discussed in the previous section.

The features of all five dummy cores are summarized in Table 5.5.

Table 5.5: Summary of features/parameters of five dummy authenticated ciphers and their high-speed implementions

|        | CIPH  | Npub | AD    |       | PT    |      | Tag Off- |       | Pre-Processor |         |

|--------|-------|------|-------|-------|-------|------|----------|-------|---------------|---------|

|        | EXP?  | Size | Block | Pad?  | Block | Pad? | Size     | line? | Data          | Key     |

|        |       |      | size  |       | size  |      |          |       | buffer?       | buffer? |

| dummy1 | False | 96   | 128   | True  | 128   | True | 128      | False | True          | True    |

| dummy2 | False | 128  | 96    | False | 128   | True | 128      | True  | True          | True    |

| dummy3 | True  | 128  | 128   | True  | 128   | True | 128      | False | True          | True    |

| dummy4 | False | 128  | 32    | True  | 32    | True | 64       | False | False         | True    |

| dummy5 | False | 128  | 32    | True  | 32    | True | 128      | False | False         | False   |

#### 5.4.1 dummy1

This example is aimed at presenting the behavior of the Pre- and Post-processors for a typical CipherCore. The following parameters are used:

- $AD_{block\_size} = PT_{block\_size} = 128$  bits

- $Npub_{size} = 96$  bits

- $Pad(AD_n) = AD_n$  if  $len(AD_n) = block\_size$  else  $AD_n||10^*$

- $Pad(PT_m) = PT_m$  if  $len(PT_m) = block$  size else  $PT_m||10^*$

- CIPH\_EXP=False

#### 5.4.2 dummy2

This example aims at presenting the behavior of the PreProcessor when  $AD_{block\_size} \neq PT_{block\_size}$ , and zero padding is applied to AD. The following parameters are used:

- $AD_{block\ size} = 96$  bits

- $PT_{block\_size} = Npub_{size} = 128$  bits

- $Pad(AD_n) = AD_n$  if  $len(AD_n) = block\_size$  else  $AD_n||0^*$

- $Pad(PT_m) = PT_m$  if  $len(PT_m) = block\_size$  else  $PT_m||10^*$

- $\bullet \ \ \mathbf{CIPH} \underline{\quad} \mathbf{EXP} \mathrm{=} \mathbf{False}$

#### 5.4.3 dummy3

This example aims at presenting an example implementation for algorithms that have ciphertext expansion. The following parameters are used:

- $AD_{block\ size} = PT_{block\ size} = Npub_{size} = 128$  bits

- $Pad(AD_n) = AD_n$  if  $len(AD_n) = block\_size$  else  $AD_n||10^*$

- $Pad(PT_m) = PT_m$  if  $len(PT_m) = block\_size$  else  $PT_m||10^*$

- CIPH EXP=True

Additionally, the Len segment is removed from the tag generation for this dummy core, so the new equation for Tag is

$$Tag = Key \oplus Npub \oplus \bigoplus_{i=1}^{n-1} AD_i \oplus Pad(AD_n) \oplus \bigoplus_{i=1}^{m-1} PT_i \oplus Pad(PT_m)$$

(5.8)

#### 5.4.4 dummy4

This example aims at presenting the behavior of the Pre- and Post-processor for the following cases:

- External public bus size is equal to the internal data bus size, i.e., W = DBLK\_SIZE. This allow the PreProcessor to operate in the non-registered mode for the bdi input.

- Tag size is larger than the data bus size, i.e., TAG\_SIZE > DBLK\_SIZE.

- Npub size is larger than the data bus size.

For this example, the same padding rules as those used in *dummy1* are applied, together with the following values of parameters:

- $AD_{block\_size} = PT_{block\_size} = 32$  bits

- $Npub_{size} = 128$  bits

- Key = 128 bits

- Tag = 64 bits.

31

Additionally, the ciphertext and the tag are described as followed:

$$CT_i = PT_i \oplus i \oplus KN$$

(5.9)

for  $i = 1..m - 1$ .

$$CT_m = Trunc(PT_m \oplus m \oplus KN, PT_m)$$

(5.10)

$$Tag_{63..32} = KN \oplus \bigoplus_{i=1}^{n-1} AD_i \oplus Pad(AD_n) \oplus \bigoplus_{i=1}^{m-1} PT_i \oplus Pad(PT_m) \quad (5.11)$$

$$Tag_{31..0} = \bigoplus_{i=1}^{n-1} AD_i \oplus Pad(AD_n) \oplus \bigoplus_{i=1}^{m-1} PT_i \oplus Pad(PT_m)$$

(5.12)

where,

$$KN = Key_{127..96} \oplus Key_{95..64} \oplus Key_{63..32} \oplus Key_{31..0}$$

$\oplus Npub_{127..96} \oplus Npub_{95..64} \oplus Npub_{63..32} \oplus Npub_{31..0}$

#### 5.4.5 dummy5

This example uses the same algorithm as dummy4 except that the hardware implementation relies on a different PreProcessor settings. In particular, the key bus size (KEY\_SIZE) is set to the same width as sdi bus size (SW). As a result, the PreProcessor operates in a non-registered mode for the key as well as the bdi input. This mode reduces the AEAD overall resource utilization as the key is not buffered inside the PreProcessor.

#### 5.5 AES and Keccak Permutation F

Additional support is provided for designers of cipher cores of CAESAR candidates based on AES and Keccak. Fully verified VHDL codes, block diagrams, and ASM charts of AES and Keccak Permutation F have been developed and made available at [?]. Our AES core implements a basic iterative architecture of a block cipher, with the SubBytes operation realized

# CHAPTER 5. CIPHERCORE DEVELOPMENT FOR HIGH-SPEED IMPLEMENTATIONS 32

using memory. Either distributed memory (implemented using multipurpose LUTs) or block memory is inferred depending on the specific options of FPGA tools.

### 6 Test Vector Generation

Test vectors for the targeted algorithm can be generated using our test vector generator (aeadtvgen) available in the software folder of our development package. The program relies on a reference software implementation located at \$ROOT/softare/CAESAR/\$algorithm/ref that uses the CAESAR software API to create a shared library used by our program, where \$algorithm is algorithm's name/implementation. A limited set of reference C implementations of Round 2 CAESAR candidates is provided as part of our development package.

In the case that the targeted algorithm is not available as part of our package, the user can add a new algorithm at the location noted above, and perform a slight modification to the source code. In particular, user must include an additional header file (dll.h) located in the \$REPO/software/CAESAR folder as well as prepend an *EXPORT* syntax to CAESAR software API, e.g.:

```

#include "../../dll.h"

EXPORT int crypto_aead_encrypt(..) { ... }

EXPORT int crypto_aead_decrypt(..) { ... }

```

Note: For the installation procedure of the recommended software, please refer to Appendix B.

A standard procedure for creating the testbench can be executed as follows:

- 1. Create shared CAESAR libraries (\*.dll in Windows and \*.so in Linux)

- a) In console, navigate to the CAESAR folder (\$root/software/CAESAR). Note: For Windows, perform this step using msys console

- b) Modify *Makefile* to include only targeted primitive(s).

c) (Situational) An algorithm may require OpenSSL library in order to compile. If it does, one needs to provide an appropriate compilation flag inside the following clause:

```

ifeq ($(OS),Windows_NT)

...

else

...

endif

```

Note: The flags are available but uncommented by default.

d) type

```

make

```

2. Generate the script using aeadtygen python program. The user can directly use the program from a command line or create a script similar to examples shown in \$root/software/aeadtygen/examples folder. Full description of the program can be found by typing

```

python -m aeadtvgen -h

```

3. Copy the three generated test vectors (pdi.txt, sdi.txt and do.txt) to simulation folder.

### 7 Simulation

Once test vectors are generated, copy them into your simulation folder and ensure that the PWIDTH and SWIDTH generics of the testbench are set to W and SW, respectively.

Simulation is performed until end-of-file is reached or a mismatched between expected output and output data occurs. A clock signal is deactivated when either of the conditions apply. In the case that user wants to ignore the simulation mismatch, one can set the STOP\_AT\_FAULT generic to False and the testbench will ignore the verification error.

In the case that the target implementation is ASIC, one can simulate the design by setting ASYNC\_RSTN to *True*.

Finally, four test modes, summarized in Table 7.1, are provided to simulate the conditions when available of source or target communication modules are intermittent. The rate at which the data is not available can be configured using TEST\_ISTALL and TEST\_OSTALL for input and output (in cycles), respectively.

Table 7.1: Test modes

| Value | Description                      |

|-------|----------------------------------|

| 0     | Always available                 |

| 1     | Input & Output intermittent test |

| 2     | Input intermittent test          |

| 3     | Output intermittent test         |

# 8 Generation and Publication of Results

Generation of results is possible for AEAD and CipherCore. We strongly recommend generating results primarily for AEAD. This recommendation is based on the fact that CipherCore has an incomplete functionality and a full-block-width interface.

In case AEAD, for Virtex 7 and Zynq, we recommend generating results using Xilinx Vivado [3], operating in the Out-of-Context (OOC) mode [4]. In this mode, no pin limit applies. For Virtex 6 and below, since Xilinx ISE must be used, and the OOC mode is not supported by this tool, we recommend using a simple wrapper, with five ports: clk, rst, sin, sout, piso mux sel, provided as a part of supporting files [2].

In case of CipherCore, because of a large number of port bits and limited effectiveness of the OOC mode, we recommend using the aforementioned five-port wrapper for all FPGA families.

In terms of optimization of tool options, for Virtex 7 and Zynq, we recommend the use of 25 default optimization strategies available in Xilinx Vivado. The corresponding scripts, used to run Xilinx Vivado in batch mode, are included in our supporting codes [2], and their use is explained in detail in Appendix E. For Virtex 6 and below, we recommend using Xilinx ISE and ATHENa [5]. For Altera FPGAs, we suggest using Altera Quartus II and ATHENa.

Our database of results for authenticated ciphers is available at [6]. After receiving an account in the database, the designers can enter results by themselves.

# A The Supporting Package Description

The contents of our development package is shown in Table A.1.

Table A.1: Directory structure of the development package

|             | Folder                   | Files                        | Description                                                                 |

|-------------|--------------------------|------------------------------|-----------------------------------------------------------------------------|

| scripts     | VivadoBatch              |                              | Directory that contains a set of scripts for result generation using Vivado |

|             | ModelSim                 | modelsim.tcl                 | modelsim script to run a reference design                                   |

|             | AFTVøen                  | AETVgen.py                   | Test vector generator program                                               |

|             | TITT ABOUT               | gen.py                       | Example usage                                                               |

| software    | CAESAR/                  |                              | Directory that contains an implementation of a                              |

|             | ${ m \{algorithm\}/ref}$ |                              | specific algorithm of CAESAR candidate from SUPERCOP distribution           |

|             |                          | AEAD.vhd                     | Entity only file of AEAD                                                    |

|             |                          | AEAD_Arch.vhd                | Architecture only file of AEAD                                              |

|             |                          | CipherCore.vhd               | CipherCore template                                                         |

|             |                          | AEAD_TP.vhd                  | Entity only file of Two-Pass AEAD                                           |

|             | $ m AEAD/src\_rtl\_hs$   | AEAD_Arch_TP.vhd             | Architecture only file of Two-Pass AEAD                                     |

|             |                          | CipherCore_TP.vhd            | Two-Pass CipherCore template                                                |

|             |                          | fwft_fifo.vhd                | First-Word-Fall-Through FIFO                                                |

|             |                          | PostProcessor.vhd            | PostProcessor file                                                          |

|             |                          | PreProcessor.vhd             | PreProcessor file                                                           |

|             | $ m AEAD/src\_rtl\_lw$   | AEAD.vhd                     | Top-level template file for lightweight hardware                            |

|             |                          |                              | design.                                                                     |

| hardware    | $ m AEAD/src\_tb$        | AEAD_TB.vhd                  | Universal testbench file                                                    |

| TIGITA WALE |                          | AEAD_TP_TB_Wrapper.vhd       | Wrapper file to use with the test of Two-Pass AEAD                          |

|             |                          | std_logic_1164_additions.vhd | Additional simulation package                                               |

|             | $ m AEAD/src\_rtl$       | AEAD_Wrapper.vhd             | Wrapper file for implementation of AEAD                                     |

|             | /wrappers                | CipherCore_Wrapper.vhd       | Wrapper file for implementation of CipherCore                               |

|             |                          | AEAD_TP_Wrapper.vhd          | Wrapper file for implementation of Two-Pass AFAD                            |

|             |                          | CipherCore TP Wrapper.vhd    | Wrapper file for implementation of Two-Pass Ci-                             |

|             |                          |                              | pherCore                                                                    |

|             | dummy*                   | KAT                          | Known-Answer-Test folder for dummy design                                   |

|             |                          | src_rtl                      | Reference dummy related code                                                |

|             |                          | scripts                      | ModelSim script folder to perform a quick simulation                        |

|             |                          |                              |                                                                             |

### B Installation of Libraries and Tools

#### B.1 Interpreter and compiler

#### B.1.1 Windows

#### • MinGW with MSYS as a compiler

Download and install the latest version from http://www.mingw.org. MSYS should be included in the installation package.

Note: MSYS is the console for MinGW in Windows

Below is an example in how to compile the program using MingW with Msys console (MingW shell).

cd /c/Downloads/GMU\_API\_v20/software/CAESAR

#### • Python v3.5+

Download and install the latest Python distribution package from https://www.python.org.

Note: Please make sure that all installations are done as an administrator and the path to python is correctly set in the environmental variable.

#### B.1.2 Linux

• Python v3.5+

#### B.2 OpenSSL Installation

- 1. Download and uncompress the latest version of OpenSSL

- 2. Navigate to download folder and uncompress files

- a) Open terminal (Msys console for Windows)

- b) Navigate to the download folder

- Windows

cd /c/Users/\$USER/Downloads/openssl-1.0.2e

• Linux Open terminal

cd /home/\$USER/Downloads

c) Uncompress downloaded file, e.g.

tar -zxvf openssl-1.0.2e.tar.gz

d) Change working directory

cd openssl-1.0.2e

- e) Configure OpenSSL

- Windows

./Configure mingw --prefix=/usr/local shared

Note: Possible error

"gcc command not found" error

This is caused by a problem during installation where your MingW's /bin folder is not included as a part of environmental variable. You can either try to re-install or add the variable manually. To do this manually

- i. Access environmental variable on Windows system, right-click @ My Computer (or This PC on some system) -> Properties -> Advanced System Settings -> Advanced Tab -> Environmental Variables

- ii. Prepend C:/MingW/bin; to PATH variable by editing PATH variable in either  $User\ variable\ for\ \$USER$  or  $System\ variable$ .

iii. OK -> Apply

• Linux

./Configure --prefix=/usr/local shared

f) Compile and install

make && make install

### B.3 Python module (aeadtvgen)

The distribution package for aeadtvgen can be found as a wheel (\*.whl) package under \$root/software/aeadtvgen/dist folder. To install, type

python -m pip install \_PACKAGED\_MODULE\_.whl

### Bibliography

- [1] Cryptographic Engineering Research Group (CERG) at GMU. (2016, June) CAESAR Hardware API, full specification. [Online]. Available: https://cryptography.gmu.edu/athena/index.php?id=download

- [2] —. (2016, June) Development Package for the CAESAR Hardware API. [Online]. Available: https://cryptography.gmu.edu/athena/index.php?id=download

- [3] Xilinx. Vivado Design Suite. [Online]. Available: http://www.xilinx.com/products/design-tools/vivado.html

- [4] —, Vivado Design Suite User Guide: Hierarchical Design, April 2015. [Online]. Available: http://www.xilinx.com/support/documentation/sw manuals/xilinx2015 1/ug905-vivado-hierarchical-design.pdf

- [5] K. Gaj, J.-P. Kaps, V. Amirineni, M. Rogawski, E. Homsirikamol, and B. Y. Brewster, "ATHENa automated tool for hardware evaluation: Toward fair and comprehensive benchmarking of cryptographic hardware using FPGAs," in 20th International Conference on Field Programmable Logic and Applications FPL 2010. IEEE, 2010, pp. 414–421.

- [6] Cryptographic Engineering Research Group (CERG) at GMU. (2016, June) GMU ATHENa Database of Results. [Online]. Available: https://cryptography.gmu.edu/athenadb/fpga\_auth\_cipher/rankings\_view